top of page

Chip Design Expert Advisory

Strong chip design capabilities are key to turning innovative idea into real products. FiCCC provides expert coaching and consultation, helping companies explore new technologies, enhance design practices, and gain the confidence to develop their ideas further.

FiCCC offers tailored support for companies planning to design custom integrated circuits (IC), particularly when adopting advanced or unfamiliar technologies (SoC, edge AI, RF, low-power CMOS, SiP integration). Coaching focuses on system-level architecture, functional partitioning, node selection, and early-stage project scoping. All done in collaboration with well-known partners.

What do we want to achieve together

-

Clarified scope and design intent for new IC project

-

Technical strategy tailored to company’s application domain

-

Inputs to partner selection and toolchain needs

-

Higher-quality project proposals for national/EU R&D funding

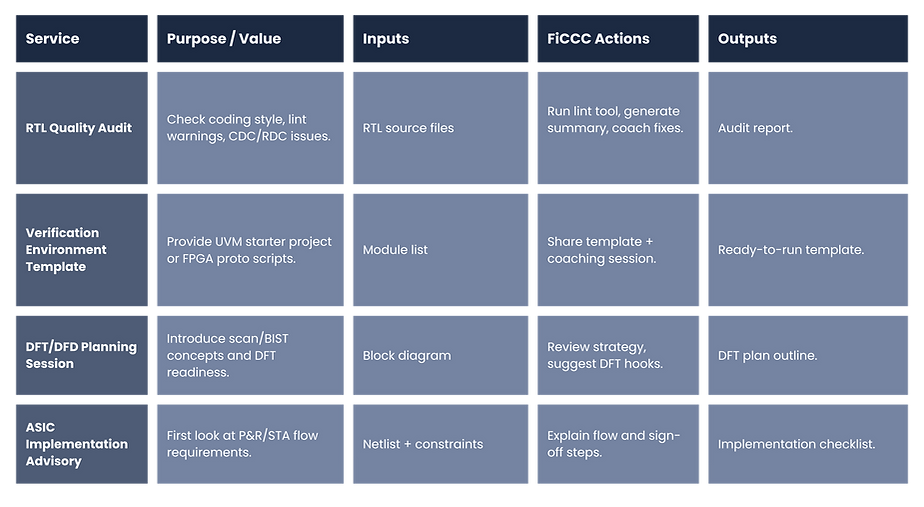

Design Advisory service level categories

Our services for Design Excellence

The services include but are not limited to:

Analog IC design services

.png)

RF IC design services

Mixed-Signal IC design services

Digital IC design services

.png)

MEMS/Sensor design services

Integration & cross-domain support services

.png)

bottom of page